|

<< Click to Display Table of Contents >> Basic PWM |

|

|

<< Click to Display Table of Contents >> Basic PWM |

|

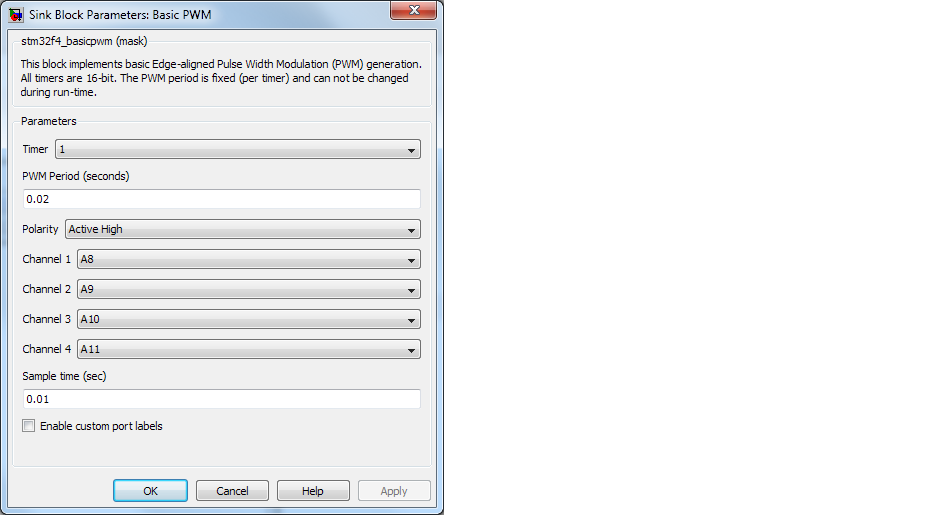

Use this block to generate edge-aligned Pulse Width Modulation (PWM) signals. The following conditions applies.

| 1. | Up to a maximum number of 4 edge-aligned PWM signals (channels) can be generated per timer. |

| 2. | Each timer has 16-bit counter that determines the PWM period. |

| 3. | PWM period can not be changed during run-time. |

The following table lists available Timer and associated PWM channels together with corresponding MCU Port-Pins.

TIMER |

CH |

STM32F405RG (LQFP64) |

STM32F405OG (WLCSP90) |

STM32F405OE (WLCSP90) |

STM32F405VG (LQFP100) |

STM32F405ZG (LQFP144) |

STM32F407VE (LQFP100) |

STM32F407VG (LQFP100) |

STM32F407ZE (LQFP144) |

STM32F407ZG (LQFP144) |

STM32F407IE (UFBGA176) |

STM32F407IE (LQFP176) |

STM32F407IG (UFBGA176) |

STM32F407IG (LQFP176) |

STM32F415RG (LQFP64) |

STM32F415OG (WLCSP90) |

STM32F415VG (LQFP100) |

STM32F415ZG (LQFP144) |

STM32F417VE (LQFP100) |

STM32F417VG (LQFP100) |

STM32F417ZE (LQFP144) |

STM32F417ZG (LQFP144) |

STM32F417IE (UFBGA176) |

STM32F417IE (LQFP176) |

STM32F417IG (UFBGA176) |

STM32F417IG (LQFP176) |

1 |

1 |

|

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

|

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

PE9 |

1 |

1 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

PA8 |

1 |

2 |

|

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

|

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

PE11 |

1 |

2 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

PA9 |

1 |

3 |

|

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

|

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

PE13 |

1 |

3 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

PA10 |

1 |

4 |

|

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

|

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

PE14 |

1 |

4 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

PA11 |

2 |

2 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

PB3 |

2 |

3 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

2 |

3 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

PB10 |

2 |

4 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

2 |

4 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

PB11 |

3 |

1 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

3 |

1 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

3 |

1 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

PB4 |

3 |

2 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

3 |

2 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

3 |

2 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

PB5 |

3 |

3 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

PB0 |

3 |

3 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

3 |

4 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

PB1 |

3 |

4 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

4 |

1 |

|

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

|

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

PD12 |

4 |

1 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

PB6 |

4 |

2 |

|

|

|

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

|

|

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

PD13 |

4 |

2 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

PB7 |

4 |

3 |

|

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

|

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

PD14 |

4 |

3 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

4 |

4 |

|

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

|

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

PD15 |

4 |

4 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

5 |

1 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

PA0 |

5 |

1 |

|

|

|

|

|

|

|

|

|

PH10 |

PH10 |

PH10 |

PH10 |

|

|

|

|

|

|

|

|

PH10 |

PH10 |

PH10 |

PH10 |

5 |

2 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

PA1 |

5 |

2 |

|

|

|

|

|

|

|

|

|

PH11 |

PH11 |

PH11 |

PH11 |

|

|

|

|

|

|

|

|

PH11 |

PH11 |

PH11 |

PH11 |

5 |

3 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

5 |

3 |

|

|

|

|

|

|

|

|

|

PH12 |

PH12 |

PH12 |

PH12 |

|

|

|

|

|

|

|

|

PH12 |

PH12 |

PH12 |

PH12 |

5 |

4 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

5 |

4 |

|

PI0 |

PI0 |

|

|

|

|

|

|

PI0 |

PI0 |

PI0 |

PI0 |

|

PI0 |

|

|

|

|

|

|

PI0 |

PI0 |

PI0 |

PI0 |

8 |

1 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

PC6 |

8 |

1 |

|

|

|

|

|

|

|

|

|

PI5 |

PI5 |

PI5 |

PI5 |

|

|

|

|

|

|

|

|

PI5 |

PI5 |

PI5 |

PI5 |

8 |

2 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

PC7 |

8 |

2 |

|

|

|

|

|

|

|

|

|

PI6 |

PI6 |

PI6 |

PI6 |

|

|

|

|

|

|

|

|

PI6 |

PI6 |

PI6 |

PI6 |

8 |

3 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

PC8 |

8 |

3 |

|

|

|

|

|

|

|

|

|

PI7 |

PI7 |

PI7 |

PI7 |

|

|

|

|

|

|

|

|

PI7 |

PI7 |

PI7 |

PI7 |

8 |

4 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

PC9 |

8 |

4 |

|

|

|

|

|

|

|

|

|

PI2 |

PI2 |

PI2 |

PI2 |

|

|

|

|

|

|

|

|

PI2 |

PI2 |

PI2 |

PI2 |

9 |

1 |

|

|

|

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

|

|

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

PE5 |

9 |

1 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

PA2 |

9 |

2 |

|

|

|

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

|

|

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

PE6 |

9 |

2 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

PA3 |

10 |

1 |

|

|

|

|

PF6 |

|

|

PF6 |

PF6 |

PF6 |

PF6 |

PF6 |

PF6 |

|

|

|

PF6 |

|

|

PF6 |

PF6 |

PF6 |

PF6 |

PF6 |

PF6 |

10 |

1 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

PB8 |

11 |

1 |

|

|

|

|

PF7 |

|

|

PF7 |

PF7 |

PF7 |

PF7 |

PF7 |

PF7 |

|

|

|

PF7 |

|

|

PF7 |

PF7 |

PF7 |

PF7 |

PF7 |

PF7 |

11 |

1 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

PB9 |

12 |

1 |

|

|

|

|

|

|

|

|

|

PH6 |

PH6 |

PH6 |

PH6 |

|

|

|

|

|

|

|

|

PH6 |

PH6 |

PH6 |

PH6 |

12 |

1 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

PB14 |

12 |

2 |

|

|

|

|

|

|

|

|

|

PH9 |

PH9 |

PH9 |

PH9 |

|

|

|

|

|

|

|

|

PH9 |

PH9 |

PH9 |

PH9 |

12 |

2 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

PB15 |

13 |

1 |

|

|

|

|

PF8 |

|

|

PF8 |

PF8 |

PF8 |

PF8 |

PF8 |

PF8 |

|

|

|

PF8 |

|

|

PF8 |

PF8 |

PF8 |

PF8 |

PF8 |

PF8 |

13 |

1 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

PA6 |

14 |

1 |

|

|

|

|

PF9 |

|

|

PF9 |

PF9 |

PF9 |

PF9 |

PF9 |

PF9 |

|

|

|

PF9 |

|

|

PF9 |

PF9 |

PF9 |

PF9 |

PF9 |

PF9 |

14 |

1 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

PA7 |

This block accepts Input Duty Cycle (%) between 0-100 as double values for each generated PWM signal.

This block supports "Enable custom port labels".

PWM signal frequency is determined by the value TIMx_ARR and a duty cycle is determined by the value TIMx_CCRx. The timer's clock is computed as follows:

TIMx_CLK = HCLK/APBxPrescaler

where TIM2,3,4,5,6,7,12,13,14 uses APB1 and TIM1,8,9,10,11 uses APB2.

The timer's auto reload value (TIMx_ARR) that determines the PWM period for each timer is computed from:

TIMx_ARR = (TIMx_CounterClock * PWM_period) - 1

where TIMx_CounterClock = TIMx_CLK / (TIMx_Prescaler + 1).

STM32F4 Target searches for the optimal TIMx_ARR automatically using the following constraints

| 1. | TIMx_Prescaler <= 65535 |

| 2. | TIMx_ARR is as near a whole number as possible, i.e. min(TIMx_ARR - floor(TIMx_ARR)) |

The duty cycle is computed from:

TIMx_CCRx = TIMx_ARR * (Duty Cycle / 100)